ciss电容是什么意思,mos管的ciss-KIA MOS管

信息来源:本站 日期:2025-07-25

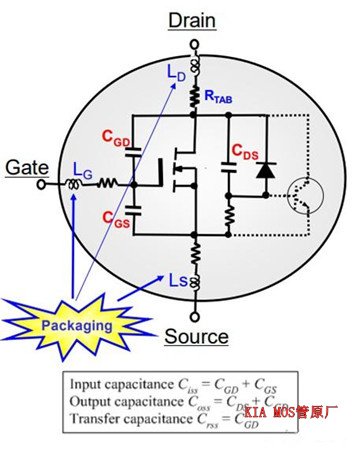

定义:输入电容是栅极与源极、漏极之间的总电容,由栅源电容(Cgs)和栅漏电容(Cgd)并联而成,即Ciss = Cgs + Cgd。

作用:输入电容影响MOS管的开关速度。当输入电容充电至阈值电压时,器件才能开启;放电至一定值时,器件才能关断。因此,驱动电路和Ciss对器件的开启和关断延时有着直接的影响。

Ciss输入电容详解

这是当漏源短接时测得的栅极到源极之间的总电容,它等于栅源电容Cgs加上栅漏电容Cgd。这个参数对于驱动电路的设计至关重要,因为它决定了驱动器需要提供的最大充电电流,以确保MOSFET能够快速开启或关闭。

Ciss反映栅极驱动电路需充/放电的总电荷量,直接影响MOSFET的开关速度。当Ciss较大时,栅极充电时间延长,开关延迟增加,同时驱动电流需求更高。

Ciss电容直接影响开关的上升时间和下降时间,因为栅极电压的变化需要通过外部驱动电路对Ciss充电。

测量条件:通常在规格书中,Ciss是在特定的漏源电压(Vds)和栅源电压(Vgs)下测得的(例如Vgs=0V,Vds=25V,f=1MHZ)。

应用影响:较大的Ciss意味着需要更大的栅极驱动电流或更长的充电时间,从而可能降低开关速度。在高频应用中,Ciss较小的MOSFET更受欢迎。

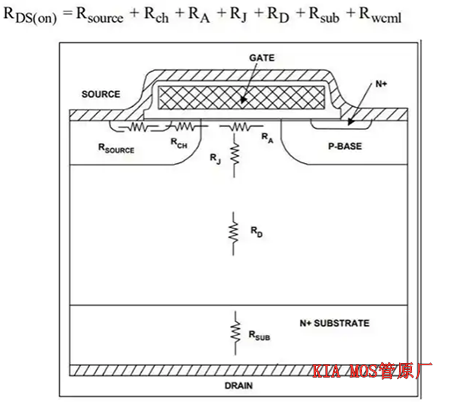

不同的MOSFET结构对寄生电容特性的影响

平面型MOSFET(Planar MOSFET):传统的构造方式,具有相对较大的Coss值,因此更适合低频应用。这类器件的制造工艺较为成熟,成本较低,但在高频应用中表现不如其他类型。

沟槽型MOSFET(Trench MOSFET):通过减少单元面积内的有效栅长来降低Ciss和Crss,从而提高了工作频率上限。沟槽型MOSFET可以在较小的芯片尺寸下实现更低的导通电阻和更好的热性能,但同时也面临着栅氧化层应力的问题。

屏蔽栅MOSFET(Shielded Gate MOSFET, SGT):引入了额外的屏蔽层来减小Cgd,进而优化了开关特性并降低了噪声敏感度。这种结构有助于改善MOSFET的抗干扰能力和可靠性。

超结MSOFET(Super Junction MOSFET, SJ):采用特殊的掺杂技术,在保持低导通电阻的同时大幅减少了Coss,非常适合用于高效率转换器中。超结结构允许更高的击穿电压,同时保持较低的导通电阻,这对于提高电源转换效率非常有利。

联系方式:邹先生

座机:0755-83888366-8022

手机:18123972950(微信同号)

QQ:2880195519

联系地址:深圳市龙华区英泰科汇广场2栋1902

搜索微信公众号:“KIA半导体”或扫码关注官方微信公众号

关注官方微信公众号:提供 MOS管 技术支持

免责声明:网站部分图文来源其它出处,如有侵权请联系删除。